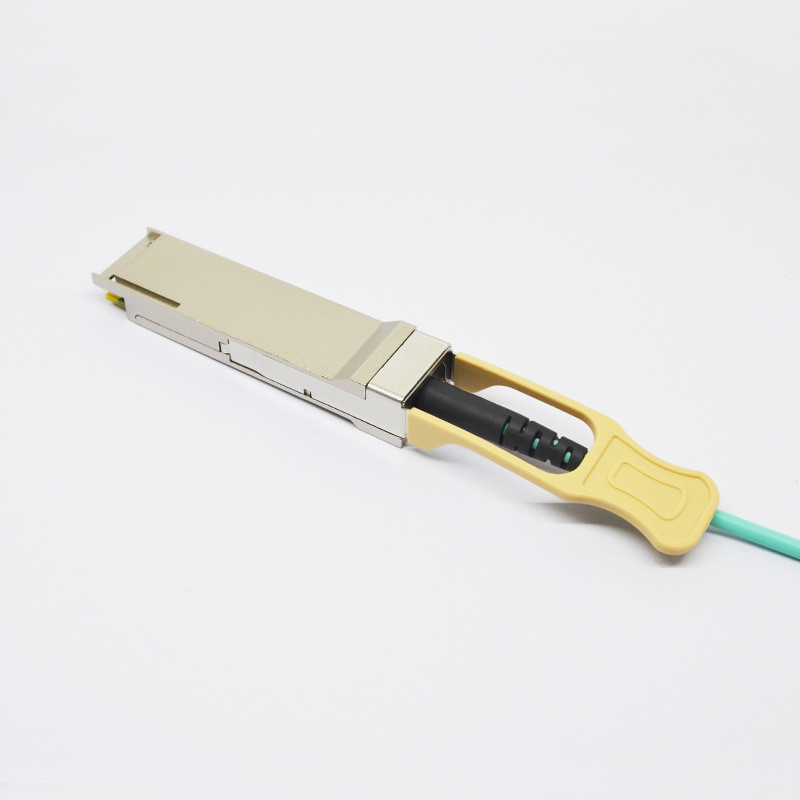

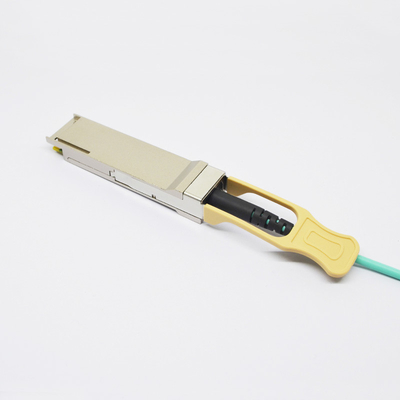

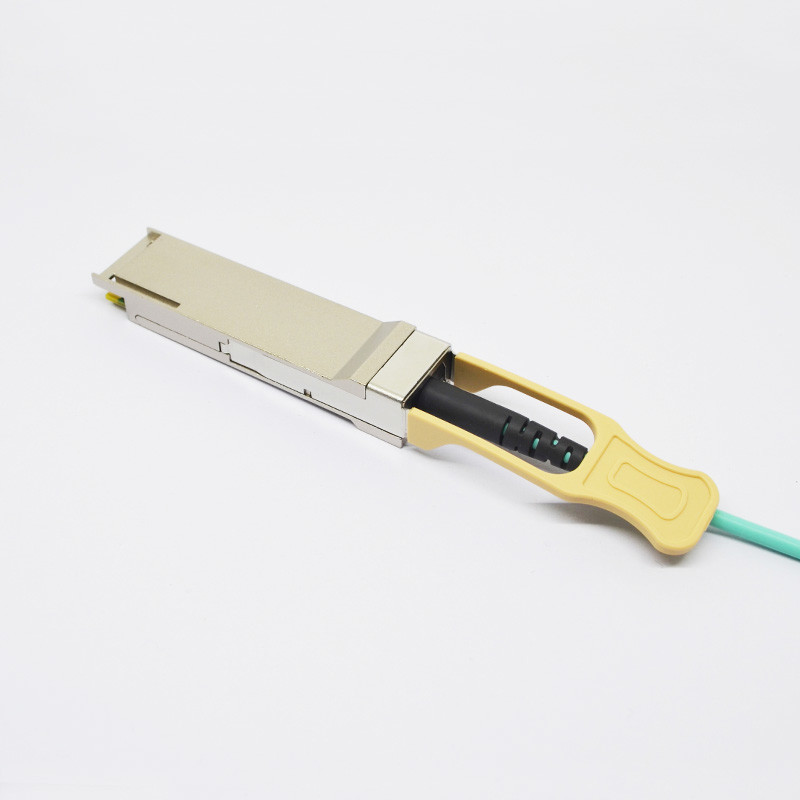

적합한 100G QSFP28 부동태 동 케이블 3M AOC 케이블 쥬니퍼

쥬니퍼 네트워크와 호환가능한 100G QSFP28 JNP-QSFP28-AOC-3M 활동적 광케이블

기술 :

QSFP28 활동적 광케이블 (AOC) 성분은 100GB 이더넷 응용을 위해 설계됩니다. 100GbE 장치가 전기적이고 기계적인 상술을 기반으로 매우 높은 포트 밀도로 설계되도록 그것은 설계됩니다. 애플리케이션은 레인마다 25.781Gbps에 100G AOC QSFP28 애플리케이션과 100GBASE-SR4입니다.

광학적 특성 (70 C에 대한 상부(C) = 0, 3.47 V에 대한 VCC = 3.13)

| 매개 변수 |

기호 |

민. |

Typ |

맥스. |

유닛 |

기록 |

| 송신기 |

| 작동 파장 |

λ |

840 |

850 |

860 |

별거 안 해 |

|

| 출력 광학 눈 |

IEEE 0802.3ae로 순응합니다 |

| 수신기 |

| 작동 파장 |

|

840 |

|

860 |

별거 안 해 |

|

전기 특성 (70 C에 대한 상부(C) = 0, 3.47 V에 대한 VCC = 3.13)

| 매개 변수 |

기호 |

민. |

Typ |

맥스. |

유닛 |

기록 |

| 모듈셀 모듈 선택 |

VOL |

0 |

|

0.8 |

V |

|

| 모듈셀 모듈 구독해제 |

VOH |

2.5 |

|

VCC |

V |

|

| 라이피모드 낮은 파워 방식 |

VIL |

0 |

|

0.8 |

V |

|

| 라이피모드 정상적 작동 |

VIH |

2.5 |

|

VCC+0.3 |

V |

|

| 리셋들 리셋 |

VIL |

0 |

|

0.8 |

V |

|

| 리셋들 정상적 작동 |

VIH |

2.5 |

|

VCC+0.3 |

V |

|

| 모듈프스들 정상적 작동 |

VOL |

0 |

|

0.4 |

V |

|

| IntL 일시정지 |

VOL |

0 |

|

0.4 |

V |

|

| IntL 정상적 작동 |

VOH |

2.4 |

|

VCC |

V |

|

| 활동적 케이블 인풋 전기 특성 |

| 차분 데이터 입력 전압 |

VIH-VIL |

200 |

|

1600 |

음피피 |

1 |

| 차동 입력 임피던스 |

린 |

90 |

100 |

110 |

Ω |

|

| TX 불 가능 입력 저전압 |

VIL |

0 |

|

0.8 |

V |

2 |

| TX 불 가능 입력 전압 높은 것 |

VIH |

2.0 |

|

VCC |

V |

2 |

| TX 결점 출력 저전압 |

VOL |

0 |

|

0.8 |

V |

3 |

| TX 결점 출력 전압 최고 |

VOH |

2.0 |

|

VCC |

V |

3 |

기록 :

1. 평균 마력 수치들은 IEEE 802.3ae마다, 단지 정보를 제공합니다.

2. 계속하여 BER 1E-12 이하 측정됩니다. 방법 패턴은 최악 ER=4.5@ 10.3125Gb/s로 PRBS 231-1입니다.

3. 내부 AC은 연결되었습니다

4. TX-드이사벨 프크트에 대한 10 KΩ 급상승에 내부 4.7KΩ을 가지고 있습니다

5. 호스트 보드에 프크크에 4.7KΩ 급상승으로 측정하세요

핀 설명

| 핀 |

이름 |

논리 |

기술 |

|

| 1 |

국민 총수요 |

|

땅 |

1 |

| 2 |

Tx2n |

CML-I |

송신기 역데이터 입력 |

10 |

| 3 |

Tx2p |

CML-I |

송신기 비반전 데이터 입력 |

10 |

| 4 |

국민 총수요 |

|

땅 |

1 |

| 5 |

Tx4n |

CML-I |

송신기 역데이터 입력 |

10 |

| 6 |

Tx4p |

CML-I |

송신기 비반전 데이터 입력 |

10 |

| 7 |

국민 총수요 |

|

땅 |

1 |

| 8 |

모듈셀 |

LVTTL-I |

모듈은 선택합니다 |

3 |

| 9 |

리셋들 |

LVTTL-I |

모듈 리셋 |

4 |

| 10 |

프크크 Rx |

|

+3.3V 전원 공급기 수신기 |

2 |

| 11 |

SCL |

LVCMOS-I/O |

2개의 와이어 직렬 접속 시계 |

5 |

| 12 |

SDA |

LVCMOS-I/O |

2 와이어 직렬 접속 자료 |

5 |

| 13 |

국민 총수요 |

|

땅 |

1 |

| 14 |

Rx3p |

CML-O |

수신기 비반전 데이터 출력 |

9 |

| 15 |

Rx3n |

CML-O |

수신기 역데이터 출력 |

9 |

| 16 |

국민 총수요 |

|

땅 |

1 |

| 17 |

Rx1p |

CML-O |

수신기 비반전 데이터 출력 |

9 |

| 18 |

Rx1n |

CML-O |

수신기 역데이터 출력 |

9 |

| 19 |

국민 총수요 |

|

땅 |

1 |

| 20 |

국민 총수요 |

|

땅 |

1 |

| 21 |

Rx2n |

CML-O |

수신기 역데이터 출력 |

9 |

| 22 |

Rx2p |

CML-O |

수신기 비반전 데이터 출력 |

9 |

| 23 |

국민 총수요 |

|

땅 |

1 |

| 24 |

Rx4n |

CML-O |

수신기 역데이터 출력 |

9 |

| 25 |

Rx4p |

CML-O |

수신기 비반전 데이터 출력 |

9 |

| 26 |

국민 총수요 |

|

땅 |

1 |

| 27 |

모듈프스들 |

LVTTL-O |

모듈 현재 |

6 |

| 28 |

IntL |

LVTTL-O |

일시정지 |

7 |

| 29 |

프크크 Tx |

|

+3.3V 전원 공급기 송신기 |

2 |

| 30 |

Vcc1 |

|

+3.3V 전원 공급기 |

2 |

| 31 |

라이피모드 |

LVTTL-I |

저전력 모드 |

8 |

| 32 |

국민 총수요 |

|

땅 |

1 |

| 33 |

Tx3p |

CML-I |

송신기 비반전 데이터 입력 |

10 |

| 34 |

Tx3n |

CML-I |

송신기 역데이터 입력 |

10 |

| 35 |

국민 총수요 |

|

땅 |

1 |

| 36 |

Tx1p |

CML-I |

송신기 비반전 데이터 |

|

| 37 |

Tx1n |

CML-I |

송신기 역데이터 입력 |

10 |

| 38 |

국민 총수요 |

|

땅 |

1 |

기록 :

1. 국민 총수요는 신호을 나타내는 상징이고 모듈을 위해 공통인 공급 (전력) 입니다. 모두는 모듈 이내에 공통이고 모든 모듈 내압이 달리 언급되지 않으면 이 잠재성에 대한 언급입니다. 직접적으로 호스트 보드 신호 공통 접지 평면에 이것들을 연결하세요.

2. 프크크 Rx, Vcc1과 프크크 Tx는 동시에 적용될 것입니다. 프크크 Rx Vcc1과 프크크 Tx는 내부로 어떠한 조합에서 모듈 내에 연결될 수 있습니다. 커넥터 핀은 각각 1000 마의 최대 전류를 위해 평가됩니다. 추천된 호스트 보드 전력 공급 필터링은 아래 보여집니다 .

3. 모듈셀은 입력 핀입니다. 호스트에 의해 낮게 잡힐 때, 사령선은 2 와이어 직렬 통신 지휘에 응답합니다. 모듈셀은 한 개의 2 와이어 인터페이스 버스에 다중 모듈의 사용을 허용합니다. 모듈셀이 높은 것일 때, 모듈은 호스트로부터 어떠한 2 유선 인터페이스 통신도 응답하거나 확인하지 않을 것입니다. 모듈셀 신호 입력 노드는 모듈에서 하이상태에 편견을 가질 것입니다. 충돌을 피하기 위해, 호스트 시스템은 어떠한 모듈도 선택해제되는 후에 모듈셀 인가 해제 시간 이내에 2 유선 인터페이스 통신을 시도하지 않을 것입니다. 유사하게, 호스트는 최근에 선택된 모듈과 통신하기 전에 모듈셀이 시간을 주장하는 색택 고정기를 적어도 기다릴 것입니다. 다른 모듈의 주장과 디어서팅 기간은 위에서 말한 타이밍 요구사항이 충족되는 한 중첩될 수 있습니다.

4. 리셋들 핀은 모듈에서 프크크에 끌려올 것입니다. 모든 사용자 모듈 설정을 그들의 디폴트 상태로 되돌리면서, 완전한 모듈이 재설정한 최소 펄스 길이 (t_Reset_init) 전문가들보다 더 오랫동안의 리셋들 핀 위의 낮은 수준. 리셋들 핀 위의 낮은 수준이 공개되는 후 모듈 리셋이 상승 에지 위의 타임즈 지 (t_init) 시작을 주장합니다. 리셋의 실행 동안 (t_init) 모듈이 리셋 인터럽트의 완료를 보여줄 때까지 호스트는 모든 상태 비트를 무시할 것입니다. 모듈은 data_not_ready 비트와 IntL 신호가 낮다고 주장하는 것에 의한 이것이 부정한 것을 나타냅니다. 모듈이 리셋을 요구하지 않고 리셋 인터럽트의 이 완료를 부쳐야 하는 (핫 삽입을 포함하여) 전원 켬 위의 그것을 주목하세요.

5. SCL과 SDA 외에 저속도 신호화는 프크크에 저전압 TTL (LVTTL) 작동을 기반으로 합니다. 프크크는 프크트스, 프크크스, vcc_host 또는 Vcc1의 일반적 공급 전압을 언급합니다.

호스트들은 각각의 2 유선 인터페이스 SCL (시계)과 SDA (데이터)과 모든 저속도 상태 출력물에 vcc_host에 연결된 풀업 저항기를 사용할 것입니다. SCL과 SDA는 버스 토폴로지를 지원할 수 있는 뜨거운 플러그 인터페이스입니다.

6. 모듈프스들은 호스트 보드에 vcc_host에 끌어 올려지고 모듈에 기초가 됩니다. 모듈프스들은 삽입하고 명백하게 되지 않은 높은 것이 모듈이 육체적으로 있을 때 호스트 커넥터를 비우세요 때 최저 선언입니다.

7. IntL은 출력 핀입니다. IntL이 낮을 때, 그것은 가능한 모듈 작동 결함 또는 호스트 시스템에 중대한 지위를 보여줍니다. 호스트는 2번 와이어 직렬 접속을 사용하여 일시정지을 얻는 원천을 확인합니다. IntL 핀은 개방 컬렉터 출력이고, 호스트 보드에 공급 전압을 주관하기 위해 당겨질 것입니다. INTL 핀은 바이트 2 비트 0 (준비되지 않은 데이터)이 '0'과 플래그 필드의 가치를 참조하는 때인 리셋의 완료가 읽히는 후에 명백하게 되지 않은 높습니다 (SFF-8636을 보세요).

8. 라이피모드 핀은 모듈에서 프크크에 끌어 올려질 것입니다. 핀은 하드웨어 제어입니다

높을 때 모듈을 저전력 모드에 넣는데 사용됩니다. power_override, power_set과 high_power_class_enable 소프트웨어 제어 비트 (연설 A0h, 바이트 93 비트 0,1,2)의 라이피모드 핀과 조합을 이용하여, 모듈이 얼마나 많은 권력을 낭비할 수 있는지를 호스트는 컨트롤합니다.

9. RX(n)(p/n)는 모듈 수신기 데이터 출력입니다. RX(n)(p/n)는 호스트 ASIC(SerDes)에 달리 100 오옴으로 종결되어야 한 ac-결합 100 오옴 차동 라인입니다. 교류 결합은 모듈 안에서 있고, 호스트 보드에 요구하지 않았습니다. 28 Gb에 있는 작전을 위해 / S 관련 규격 (예를 들면, OIF CEI v3.1은) 고속 차동 라인에 대하여 신호 요구사항을 규정합니다. 더 낮은 세율로 수술을 위해 관련 규격을 언급하세요.

기록 : 유산 QSFP의 삽입과 호스트로의 QSFP+ 모듈의 가능성 때문에

더 높은 속도 조작을 위해 설계되어 호스트 입력의 손상 문턱치가 적어도 1600의 mV 피크 투 피크 차이이라는 것이라고 권고됩니다. 광학적 입력 신호의 손실을 위한 출력 스퀄치, 앞으로 Rx 스퀄치는 요구되고, 다음과 같이 작용할 것입니다. 광학 시그널 온의 경우에 수준이하로 거나 충분한 되는 어떠한 채널도 LOS를 주장하기 위해 요구한 후, 저 채널을 위한 수신기 데이터 출력이 으깨거나 무력하게 될 것입니다. 찌부러지거나 불구가 된 출력된 상태에서 차별적 전압폭이 50 음피피 이하일 동안 임피던스 레벨은 유지됩니다. 정상 작동에서 디폴트 케이스는 활동적인 Rx 스퀄치를 가지고 있습니다. Rx 스퀄치는 2번 와이어 직렬 접속을 통하여 Rx 스켈치 불능을 사용하여 비활성화시킬 수 있습니다. Rx 스켈치 불능은 옵션 기능입니다. 세부 사항을 위해 SFF-8636을 언급하세요.

10. Tx(n)(p/n)는 모듈 송신기 데이터 입력입니다. 그들은 모듈 안에서 100 오옴 차별적 종결과 ac-결합 100 오옴 차동 라인입니다. 교류 결합은 모듈 안에서 있고, 호스트 보드에 요구하지 않았습니다. 28 Gb에 있는 작전을 위해 / S 관련 규격 (예를 들면, OIF CEI v3.1은) 고속 차동 라인에 대하여 신호 요구사항을 규정합니다. 더 낮은 세율로 수술을 위해 관련 규격을 언급하세요. 더 낮은 속도 조작을 위해 설계된 호스트로의 모듈의 삽입의 가능성 때문에, 모듈 입력의 손상 문턱치는 적어도 1600의 mV 피크 투 피크 차이일 것입니다. 입력 신호의 손실을 위한, 출력 스퀄치, 앞으로 Tx 스퀄치, 앞으로 Tx LOS는 옵션 기능입니다. 어디가 그것을 구현하 다음과 같이 작용할 것입니다. 차이의 경우에, 어떠한 채널 위의 피크 대 피크 전기 신호는 50 음피피보다 적게 되는 후, 저 채널을 위한 송신기 광 출력이 으깨거나 무력하게 될 것이고 연합하는 트스로 태극기가 졌습니다. 으깬 곳에서, 송신기 OMA는 -26 데이터 베이스 관리 프로그램보다 작거나 같고 무력하게 될 때 송신기 전력이 -30 데이터 베이스 관리 프로그램보다 작거나 같습니다. 적용을 위해, 예를 들어 송신기 오프 조건이 송신기를 무력하게 한 평균 마력의 관점에서 규정되는 이더넷은 권고되고 적용을 위해, 예를 들어 송신기 오프 조건이 송신기를 으깬 OMA의 관점에서 규정되는 인피니밴드가 권고됩니다. Tx 스퀄치가 구현되는 모듈 작동에서, 디폴트 케이스는 활동적인 Tx 스퀄치를 가지고 있습니다. Tx 스퀄치는 2번 와이어 직렬 접속을 통하여 Tx 스켈치 불능을 사용하여 비활성화시킬 수 있습니다. Tx 스켈치 불능은 옵션 기능입니다. 세부 사항을 위해 SFF 8636을 언급하세요.

케이블 기계적인 상술

| 매개 변수 |

가치 |

유닛 |

| 지름 |

3 |

Mm |

| 최소 굽힘 반지름 |

30 |

Mm |

|

길이 허용 오차

|

길이 < 1="" m:=""> |

Cm |

| 1 M ≤length ≤ 4.5 M : +15 / -0 |

Cm |

| 5 M ≤length ≤ 14.5 M : +30 / -0 |

Cm |

| Length≥15.0 M +2% / -0 |

M |

| 케이블 색 |

오렌지(OM2), 물(OM3), megenta(OM4) |

|

명령 정보

귀하의 메시지는 20-3,000 자 사이 여야합니다!

귀하의 메시지는 20-3,000 자 사이 여야합니다! 이메일을 확인하십시오!

이메일을 확인하십시오!  귀하의 메시지는 20-3,000 자 사이 여야합니다!

귀하의 메시지는 20-3,000 자 사이 여야합니다! 이메일을 확인하십시오!

이메일을 확인하십시오!